國產(chǎn)軍工芯片深度研究報告 集成電路設計的發(fā)展與挑戰(zhàn)

隨著國家安全的日益重要和軍事現(xiàn)代化的推進,國產(chǎn)軍工芯片在國防裝備中扮演著核心角色。集成電路設計作為軍工芯片研發(fā)的關(guān)鍵環(huán)節(jié),直接決定了芯片的性能、可靠性和安全性。本文基于深度研究,分析國產(chǎn)軍工芯片在集成電路設計領(lǐng)域的發(fā)展現(xiàn)狀、關(guān)鍵技術(shù)突破、面臨的挑戰(zhàn)以及未來前景。

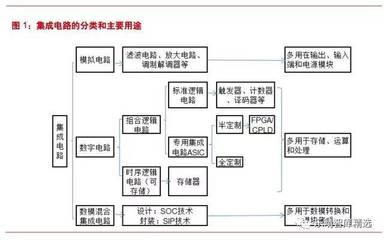

近年來,國產(chǎn)軍工芯片在集成電路設計方面取得了顯著進展。設計流程已從傳統(tǒng)的模擬電路向數(shù)字、混合信號和系統(tǒng)級芯片(SoC)方向演進。例如,在處理器設計上,國內(nèi)企業(yè)成功開發(fā)出多款基于ARM和RISC-V架構(gòu)的軍用級芯片,具備高性能、低功耗和抗干擾特性。專用集成電路(ASIC)和現(xiàn)場可編程門陣列(FPGA)的設計能力不斷提升,能夠滿足雷達、通信和導航系統(tǒng)的高可靠性需求。在設計工具方面,本土EDA(電子設計自動化)軟件的開發(fā)逐步減少對國外技術(shù)的依賴,提高了設計效率和自主可控性。

國產(chǎn)軍工芯片的集成電路設計仍面臨諸多挑戰(zhàn)。高端芯片設計依賴先進的制程工藝,而國內(nèi)在7納米及以下工藝的制造能力有限,影響了芯片的性能和集成度。設計人才短缺和研發(fā)投入不足制約了創(chuàng)新速度,尤其是在復雜系統(tǒng)芯片和人工智能芯片領(lǐng)域。供應鏈安全問題突出,關(guān)鍵IP核和材料可能受制于外部因素,需加強本土化布局。

國產(chǎn)軍工芯片的集成電路設計應聚焦于多學科融合,如結(jié)合人工智能算法優(yōu)化設計流程,提升芯片的智能化和自適應能力。同時,加強產(chǎn)學研合作,推動標準化和模塊化設計,以降低成本并加速迭代。在國家政策支持下,預計未來五年,國產(chǎn)軍工芯片將在自主知識產(chǎn)權(quán)、可靠性和應用廣度上實現(xiàn)更大突破,為國防現(xiàn)代化提供堅實支撐。

如若轉(zhuǎn)載,請注明出處:http://www.dgdxd.cn/product/5.html

更新時間:2026-03-09 13:08:38